プレスリリース

SMT部品のトレンドは極小チップ化と高機能化

キョウデン(株式会社キョウデン 本社:長野 代表取締役社長:森清隆)は電子機器の高機能及び小型化が進み高密度・高集積半導体の採用に直面する様々な課題解決に向け狭隣接実装技術を確立しました。

[画像1: https://prtimes.jp/i/88689/3/resize/d88689-3-cc139044f1cf0307687d-5.jpg ]

新製品の開発が加速する5G/6G情報端末、IoT端末、先端医療機器、非接触型サービスロボット、高速センシング技術等には、高密度・高集積化された半導体の採用が不可欠です。

今後、このような機器を取り巻く製品、モジュールの小型化は更に進展し、次世代の極小チップである0201サイズや高機能・多ピンの要求から狭ピッチ化された半導体パッケージの提案も始まっております。

また、SMT部品の小型化以外にも隣接部品との隙間も年々狭くなり、吸着ノズルが隣接部品に干渉し、不良発生を引き起こす可能性も高まる等、実装品質はより厳しい管理が必要になってきております。

これらの課題解決に向け、キョウデンはマウンタ、部品隣接間隔、メタルマスク厚と開口径、部品パットサイズ、部品レイアウト等から最適な条件を検証し、狭隣接実装技術を確立すると共に、設計時におけるシミュレーション活用と多段ビルドアップ基板製造によるトータルソリューションにより、製品の高機能・小型化を実現しました。

1.設計:解析ソリューションによるパスコン配置の最適化

高密度・高集積半導体を安定的に動作させるためには、設計時のシミュレーションを活用したバイパスコンデンサの最適配置が不可欠です。PI解析ソリューションにてバイパスコンデンサーの効果を可視化し検証します。

[画像2: https://prtimes.jp/i/88689/3/resize/d88689-3-522a87a239715d7c43d7-11.jpg ]

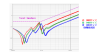

下のグラフは0201チップを狭隣接実装する事でTargetImpedanceからのマージンを確保している事が解ります。

[画像3: https://prtimes.jp/i/88689/3/resize/d88689-3-49a6641359ac434066ae-10.jpg ]

2.基板製造:高信頼の多段ビルドアップ基板製造

高速デバイスや、狭ピッチ・多ピン化が進んだ高密度・高集積半導体を搭載する小型機器には、高周波材を採用した多段ビルドアップ基板が有効です。

[画像4: https://prtimes.jp/i/88689/3/resize/d88689-3-c5eb73c105cf8e142016-13.jpg ]

3.実装:各種実装条件から確立した狭隣接実装

小型電子機器に複数の高密度・高集積半導体や極小SMD等を実装する際は、狭隣接実装に対応した設備とノウハウが必要です。

[画像5: https://prtimes.jp/i/88689/3/resize/d88689-3-bc191ee39655a4820ea9-3.png ]

[画像6: https://prtimes.jp/i/88689/3/resize/d88689-3-dfee13ee66834bf08f10-12.jpg ]

■株式会社キョウデンウェブサイト

https://www.kyoden.co.jp/

【本件に関するお問い合わせ】

株式会社キョウデン

広報部 kmori@kyoden.co.jp

プレスリリース提供:PR TIMES